### **Game Changer**

# NEUROMORPHIC COMPUTING: THE POTENTIAL FOR HIGH-PERFORMANCE PROCESSING IN SPACE

Gennadi Bersuker, Maribeth Mason, and Karen L. Jones

Artificial intelligence (AI) depends upon generating near-realtime data analysis, yet modern computers are often inefficient in the tasks of recognizing, analyzing, and classifying large volumes of information. Neuromorphic computing (NC) is intended to cover this gap by emulating certain aspects of brain functions. This brain inspired architecture, combining both computation and memory emulating neurons and synapses, has the potential to achieve the requirements of next-generation AI systems. NC technology integrates algorithms to support realtime learning with architectures built on novel computing hardware to address specific user applications.

The R&D and commercial sectors have started to advance NC capabilities in non-space applications. The space sector will likely leverage these R&D and commercial sector accomplishments as a "spin-in" technology. However, there is no easy path to adopt NC into the space sector. Satellite applications impose strict requirements—including limits on size, weight and power consumption, as well as the need for radiation-tolerance. This drives a need to develop space-resilient NC solutions. This paper explores: leading hardware innovators; specific triggers which may enable NC hardware to advance towards successful space applications; and general R&D and commercial efforts that will most likely contribute to future space sector NC innovations.

| Neuromorphic Computing: Market Readiness                                                |  |  |  |

|-----------------------------------------------------------------------------------------|--|--|--|

| Research and commercial players are focusing on development of neural processing units. |  |  |  |

| In-Space: R&D Phase, no known successful in-space demonstration.                        |  |  |  |

| Non-space: Demonstration and early market introduction phase.                           |  |  |  |

|                                                                                         |  |  |  |

| <b>Strengths</b> Drivers that might advance NC adoption                                                                | Weaknesses<br>Drivers that might delay NC adoption                                                      |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| <ul> <li>Demonstrated potential for overcoming constraints on power</li></ul>                                          | <ul> <li>Without careful coordination of efforts between algorithm,</li></ul>                           |

| and speed to enable energy efficient and agile information                                                             | architecture, and hardware experts, results may be                                                      |

| systems.                                                                                                               | suboptimal.                                                                                             |

| <ul> <li>NC could enable more efficient use of AI specific applications</li></ul>                                      | <ul> <li>Conventional architectures have a robust suite of</li></ul>                                    |

| for: object identification, change detection, autonomous control                                                       | development tools, along with large numbers of technical staff                                          |

| and decision making for a space system.                                                                                | who are trained in their use. NC will require significant funding                                       |

| • NC will support onboard adaptive learning, based on incoming data feeds when ground-based processing is unavailable. | and available researchers to advance technological progress for a range of specific space applications. |

### Introduction

Neuromorphic computing (NC) is founded on the principle that asynchronous systems can work in parallel—mimicking the efficiencies of neuro-biological architectures like our brains. In traditional computing, computation and memory read/write operations are performed sequentially. By contrast, in a neuromorphic system, asynchronous circuits containing arrays of memory elements can conduct key mathematical (multiply-accumulate) operations in parallel at the location of data, thus reducing time and power by the avoidance of moving calculated values.

Why is this a game changer? In the non-space world, there is a strong need to increase speed while reducing power consumption for data centers, smart cars and cities, the

internet of things (IoT) and a range of other distributed and near realtime mobile applications that depend on fast "intelligent" analysis of multiple data streams, which AI is intended to deliver. While we initially expect terrestrial applications to

Neuromorphic computing could emerge as a game changer for space applications where mission success relies on fast and autonomous analysis of a vast array of incoming information from multiple sources.

architectural advances are inextricably linked to the overall advancement of NC hardware in space.

#### **Neuromorphic-Inspired Architectures**

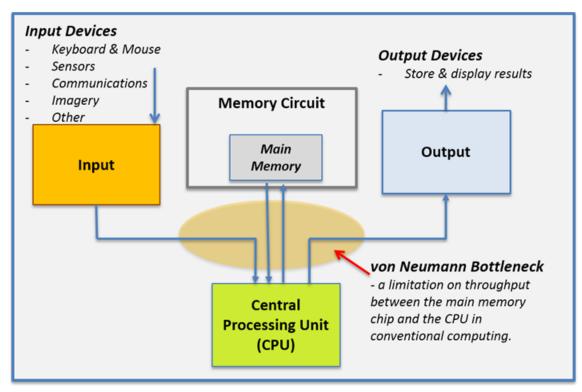

The von Neumann architecture<sup>2</sup> is the basic building block of almost all computers today. The logic cores operate sequentially by transferring data to and from an external memory unit and the central processing unit (CPU). This energy-intensive storage process, known as the "von Neumann bottleneck" presents a severe limitation for datadriven computing that requires significant memory updates (see Figure 1). By contrast, neuromorphic computing architectures combine both computation and memory through an array of neuron-like elements with synapse-like connections that can provide a significant improvement in computational capability for specific

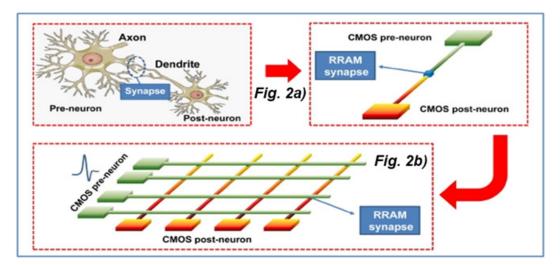

> types of analyses. Like the brain, NC has a parallel, distributed, modular, scalable, and flexible architecture (see Figure 2). Neuromorphic computers can potentially perform complex calculations faster while using less power than

harness the power of NC, it could emerge as a game changer for space applications where mission success relies on fast and autonomous analysis of a vast array of incoming information from multiple sources.

The 2018 National Defense Strategy<sup>1</sup> is the foundation for the Department of Defense's fiscal year 2019–2023 budgets to accelerate the DOD's modernization programs. The strategy notes the department's plans to "invest broadly in military applications of autonomy, artificial intelligence, and machine learning, including rapid application of commercial breakthroughs, to gain competitive military advantages." Integration of NC into future satellite systems-whether commercial, civil or defense-will depend upon future commercial breakthroughs as well as academic and government funded research initiatives which have already accelerated several commercial NC efforts (see Table 2). This paper provides an overview of the current status of R&D and commercial hardware development, and trigger events that will enable breakthroughs in NC implementation. It is important to note that algorithm development and

traditional architectures. In addition to hardware advantages, a neuromorphic platform can be fault-tolerant and can efficiently implement realtime machine learning algorithms, which may be useful in solving emerging problems in space applications, including both commercial and national security challenges. Neuromorphic computing could also advance "edge computing" capabilities. The "edge" refers to the point where data is collected and analyzed. For a satellite remote sensing system, for instance, the bulk of the computing would traditionally occur at a ground-based operations center. However, faster and more efficient data processing onboard, enabled by NC, could allow for greater autonomy and efficiency by mitigating latency and connectivity issues.

# Neuromorphic Computing Impact on Space Operations

Space missions require high-performance, reliable computing platforms that meet size, weight, and power constraints and can function in challenging environmental

Figure 1: In conventional computing the von Neumann bottleneck constrains performance due to the time and energy consumed during the required data exchange between main memory chip sets and the processor.

Figure 2: Neuronal functions are mimicked using resistive memory (resistive random-access memory or "RRAM") arrays having analog capabilities suitable for synapse operations. These architectures have achieved high-density, high-efficiency and low-power parallel signal processing. Incoming signals are modified according to the memory states thus avoiding logic-memory bottlenecks while accelerating computations.<sup>3</sup>

and operational conditions, including extreme temperature, high radiation, power loss, and disrupted communications. It is reasonable to expect that future space applications will drive the need for:

- High performance under the size, weight, and power constrains of space missions

- Data retention in the case of power loss/environmental instabilities

- On-board adaptive learning capability based on incoming external data

- Autonomous, onboard and fast data analysis to enable quicker response times

Neuromorphic processors have the potential to fulfill these requirements. In addition, neuromorphic architectures are inherently fault tolerant,<sup>4</sup> and several hardware implementations have high-radiation tolerance.<sup>5,6</sup> In addition, neuromorphic algorithms are well-suited to classes of problems of interest to the space community.<sup>5</sup>

Future applications for NC in space may include:

*Object Identification and Change Detection* – Realtime change detection of information (images, texts, voice signals, etc.) currently involves processing, filtering, and extracting massive amounts of continuously received data to interpret events and activities. While these activities have been accomplished using von Neuman architecture, NC could enable more efficient on-orbit data processing and storage, by reducing the number of bytes required to save an image and/or eliminating the need to transfer large amounts of data to a ground station for image processing.

*Autonomous Control* – Autonomous systems are critical for space-deployed remote platforms. Today the International Space Station relies upon autonomous systems for docking. The Global Exploration Roadmap (GER)<sup>7</sup> notes that "advances in electronics, computing architectures and software that enable autonomous systems to interact with humans are needed and can be leveraged from commercial markets to support maturation of needed capabilities." While NC combined with deeplearning algorithms are currently providing autonomous control capabilities to satellites, NC may introduce new advantages such as the capacity for realtime learning. As activities in space become more remote and automated, without a human in the loop, this advantage could improve the satellite's ability to analyze onboard sensor data and make better autonomous operations decisions.

*Cybersecurity* – Monitoring and assessing the cyber state of the spacecraft, are critical for ensuring mission assurance and information security. This may be particularly valuable in circumstances where communication links are jammed. Intrusion detection continually monitors communications and spacecraft bus traffic for indications of an attack underway and passes that information to the ground for situational awareness. Embedded intelligence, facilitated by NC onboard a spacecraft would provide a trusted protection mechanism.<sup>8</sup>

In many current space systems, data collected by imagers and other sensors is sent to a remote operations center for processing. This data transmission is limited in bandwidth; meanwhile, sensors continue to increase in capacity. In addition, the ability to communicate with the data collection platform may be compromised in a threat environment (e.g., a disrupted communication link). A neuromorphic processor could enable fast processing of sensor data at the point of collection and provide change detection, autonomous control and cybersecurity functions, even in threat environments. Overall, a properly designed neuromorphic platform can resolve a fundamental time-energy conundrum by delivering both fast analysis with low energy cost.

### **Market Trends and Drivers**

Emerging applications such as big data, mobile services, cloud services and the IoT require abundant computing and memory resources to generate the service and information that clients need. Neuromorphic computing is recognized by the electronics industry as a promising tool for enabling high-performance computing and ultra-low power consumption to achieve these goals.

For example, artificial intelligence services such as Siri and Alexa rely on cloud computing through an internet connection to parse and respond to spoken questions and commands. Neuromorphic chips have the potential to allow a wide variety of sensors and devices to perform intelligently without requiring an internet connection. Table 1 demonstrates market trends that drive certain applications. NC could potentially address capability gaps

| Requiring Fast, Lower Power Computation Capabilities                                                                                                                                                                                                                                                                                                          |                                                                       |                                                                                                                      |                                                                                                                                                     |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Market Trends                                                                                                                                                                                                                                                                                                                                                 | Application                                                           | Capabilities<br>Attributes/Constraints                                                                               | NC as a Gap Filler                                                                                                                                  |  |  |  |  |

| By 2018, over a third of the world's population is projected to own a smartphone, an estimated total of almost 2.53 billion smartphone users in the world. <sup>9, 1</sup>                                                                                                                                                                                    | Mobile computing                                                      | Increased performance and<br>functionality for certain tasks at<br>constant energy (constrained<br>by battery life). | NC enables edge computing—<br>providing an IT environment<br>and applications at the "edge"<br>of a cellular network or the<br>edge of any network. |  |  |  |  |

| The IoT will produce an economic impact of up to \$11.1 trillion per year by 2025. <sup>10</sup><br>The global market for robotics is growing far faster than expected and is projected to reach \$87 billion by 2025. <sup>11</sup>                                                                                                                          | Autonomous sensing,<br>multiple sensor data<br>processing and the IoT | Decreased power to allow<br>devices to perform intelligently<br>without internet connections.                        | NC enables intelligent decision<br>making by processing at the<br>device point without<br>communication to a remote<br>processor.                   |  |  |  |  |

| "Global neuromorphic computing<br>market in 2016, expanding at a<br>CAGR of 20.2% over the forecast<br>period. Increasing demand for AI<br>for language processing,<br>translation and chatterbots,<br>nonlinear controls and robotics,<br>and computer vision and image<br>processing, among others is<br>expected to drive market<br>growth." <sup>11</sup> | Increasing demand for AI                                              | Increased performance at<br>constant power density<br>(constrained by thermal<br>management).                        | NC augments traditional<br>processing with more power<br>efficient computing<br>capabilities.                                                       |  |  |  |  |

**Table 1: Market Drivers for Applications**

for cloud computing, mobile computing, and the IoT. The International Roadmap for Devices and Systems (IRDS)<sup>13</sup> is a worldwide effort that provides the physical, electrical and reliability requirements for logic and memory technologies to sustain technology growth for these market driving applications. The IRDS targets for Power-Performance-Area-Cost (PPAC) for node scaling (every two to three years) are:

*Performance* – Increase operating frequency at constant energy by 15 percent or more

*Power* – Decrease energy per switching operation at a given performance metric by 35 percent or more

Area - Reduce chip area footprint by 35 percent or more

*Cost* – Reduce die cost by 20 percent, while keeping increase in wafer cost, less than 30 percent

These scaling targets drive the industry toward major technological innovations such as emerging memories that are highly desirable for NC architectures, ensuring that high-volume manufacturing processes for NC hardware will be available. IRDS expects that these emerging memories will present a potential alternative to conventional SRAM and e-DRAM around 2021.<sup>14</sup>

# Neuromorphic Computing: Innovators and Leaders

Neuromorphic processing algorithms can be implemented using a variety of hardware platforms. They range from specialized digital and analog conventional processors

<sup>&</sup>lt;sup>1</sup>McKinsey findings based upon notion that interoperability among IoT systems is required to capture 40 percent of potential value. And that most of IoT data collected today is not used at all, and that data that are used are not fully exploited.

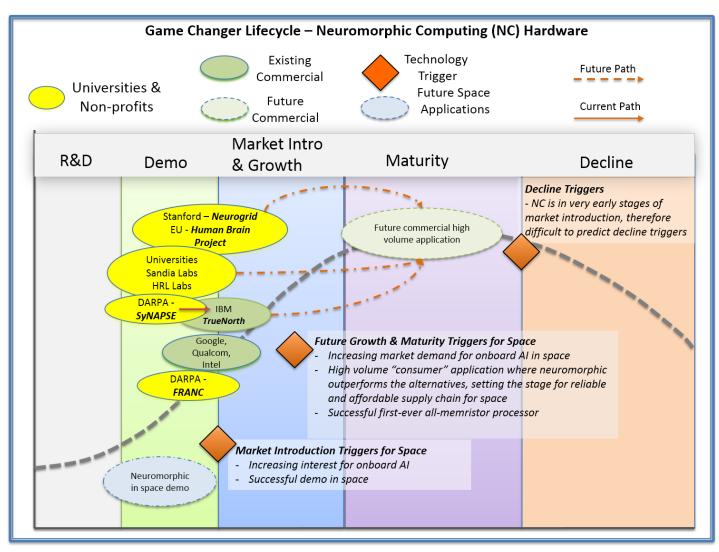

Figure 3: Game Changer Lifecycle: The field of NC is currently in the demo and R&D phase for terrestrial based commercial and R&D entities. Market maturity depends upon certain triggers. Although space applications have not yet emerged, targeted R&D investment will position NC for future space needs.

optimized for machine-learning "kernels," to systems relying on novel device materials and architectures that attempt to directly simulate an ensemble of neurons. While a large addressable market exists for highperformance computing applications, the current NC market challenge is that the hardware must be tailored to specific applications. This suggests that the end-user market must have adequate volume to justify the upfront capital investment for domain-specific NC hardware development. Yet the domain of space is generally considered to be a niche market. It is reasonable to expect; however, that the general consumer market for highperformance NC may eventually blaze the trail for followon niche level markets, such as high-performance on-orbit computing in space. A few leaders are discussed below.

# Conventional Microelectronics Implementations (CMOS Platform)

Field programmable gate arrays (FPGAs) are a commonly used platform for neuromorphic algorithm implementation and radiation hard FPGAs are commercially available.

Their programmability can be leveraged to realize a variety of network topologies, models and algorithms. They are readily available, reconfigurable, and can be optimized for specific applications. However, if the goal is

| Table 2: Hardware Implementations of Neural Networks           This table provides a list of NC innovators and stakeholders and is not comprehensive. |                                                                            |                                                                                       |                                     |                                                                                 |                                 |                                                              |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------|--|--|

| Company/<br>Project                                                                                                                                   | User<br>Applications                                                       | Energy<br>Consumption                                                                 | In-situ<br>Learning and<br>Autonomy | Implementation                                                                  | Mobility                        | Market<br>Readiness                                          |  |  |

|                                                                                                                                                       |                                                                            |                                                                                       | Commercial                          |                                                                                 |                                 |                                                              |  |  |

| 1. IBM/<br><i>TrueNorth</i>                                                                                                                           | Weather and<br>customer<br>focused<br>applications                         | High                                                                                  | No                                  | CMOS<br>processes                                                               | No                              | Fully operational product                                    |  |  |

| 2. Google (OK<br>Google)/<br>Apple (Siri)/<br>Microsoft/<br><i>Cortana</i>                                                                            | Image and<br>speech<br>recognition                                         | High                                                                                  | No, learning<br>by software         | AI software<br>running on a<br>supercomputer:<br>16,000 CPU<br>cluster (Google) | Mobile terminals for cloud comm | Demonstrated                                                 |  |  |

| 3. Qualcomm/<br><i>Zeroth</i>                                                                                                                         | Robot control                                                              | Low                                                                                   | Yes                                 | Unknown,<br>probably CMOS<br>process                                            | Yes                             | Prototype for demonstration                                  |  |  |

| 4. Intel/ <i>Loihi</i>                                                                                                                                | Image<br>recognition,<br>control of robots,<br>etc.                        | Claims up to<br>1,000 times higher<br>efficiency than<br>general purpose<br>computing | Yes                                 | 14-nm CMOS<br>process                                                           | Yes                             | Prototype, may<br>be available for<br>researchers in<br>2018 |  |  |

|                                                                                                                                                       |                                                                            | Aca                                                                                   | demic and Nonpro                    | ofit                                                                            |                                 |                                                              |  |  |

| 5. Zhejiang &<br>Hangzhou<br>Dianzi<br>Univ./ <b>Darwin</b>                                                                                           | Brain/computer<br>interface,<br>research                                   | Unknown,<br>probably high                                                             | No                                  | CMOS<br>technology                                                              | No                              | Prototype                                                    |  |  |

| 6. Stanford<br>University/<br><i>Neurogrid</i>                                                                                                        | Research on<br>human brain<br>operations                                   | High                                                                                  | No                                  | CMOS<br>processes                                                               | No                              | Operational                                                  |  |  |

| 7. Human Brain<br>Project (EU)/<br><b>BrainScaleS</b>                                                                                                 | Research,<br>simulations of<br>brain operations                            | Claims 1,000 x<br>higher efficiency<br>than traditional<br>chip                       | No                                  | Wafer-scale<br>application<br>specific<br>integrated circuit                    | No                              | Second generation chip.                                      |  |  |

| 8. Human Brain<br>Project (EU)<br>/ <b>SpiNNaker</b>                                                                                                  | Research on<br>human brain<br>operations                                   | High                                                                                  | No                                  | ARM boards/<br>custom<br>interconnect                                           | No                              | Operational,<br>accessible to<br>remote users                |  |  |

| 9. Sandia<br>National Lab/<br><i>HAANA</i>                                                                                                            | Image<br>recognition,<br>cybersecurity                                     | Low                                                                                   | Yes                                 | Memristors                                                                      | Yes                             | Prototype                                                    |  |  |

| 10. DARPA &<br>HRL Labs/<br><i>SyNAPSE</i>                                                                                                            | Video<br>recognition<br>/Control of<br>robots/drones                       | Unknown                                                                               | Yes                                 | Hybrid circuit/<br>CMOS with<br>memristors                                      | Yes                             | Prototype                                                    |  |  |

| 11. DARPA &<br>HRL Labs/<br><i>FRANC</i>                                                                                                              | Go beyond<br>Moore's law to<br>advance fast,<br>lower power<br>computation | TBD                                                                                   | TBD                                 | Exploit new<br>materials and<br>physics for fast,<br>low power<br>computation   | TBD                             | Design phase -<br>Pre-prototype                              |  |  |

to realize a small, low-power system, an FPGA may not be the correct approach. A custom application specific integrated circuit (ASIC) design will likely allow better optimization of power efficiency.

The most fully developed silicon-based neuromorphic platform is IBM's TrueNorth, which is a custom 28-nm CMOS ASIC design with strong development support.<sup>15</sup> TrueNorth emerged from the DARPA SyNAPSE program (see Figure 3). It consists of four cores that yield one million neurons and over 250 million programmable synapses. Power efficiency is obtained by running the chip at a slow clock speed, limiting computational throughput; therefore, large problems may require many chips to solve (5.4-billion-transistor chip with 4,096 cores). TrueNorth is optimized for a specific network topology, and therefore has limited programmable connectivity. It does not have efficient on-chip learning, limiting the applications for which it is useful. Some processing must be done off-chip that may quickly dominate power costs, decreasing the low-power benefit. IBM researchers had recently proposed a novel DNN implementation addressing some of the above limitations by combining conventional short-term and non-volatile long-term memories.<sup>16</sup>

The TrueNorth chip was designed with the hope of integrating brain-like capability into devices where computation is constrained by power and speed. Other silicon-based neuromorphic systems, such as SpiNNaker<sup>17</sup> (University of Manchester), Neurogrid<sup>18</sup> (Stanford) and FACETS<sup>19</sup> (University of Heidelberg) were designed with the goal of simulating large-scale neural models of the brain itself.<sup>20</sup> These systems have greatly increased the speed with which processes in the brain can be simulated and understood, and are in the early stages of becoming configurable through compiler hardware to make them useful for a wider variety of applications. In particular, SpiNNaker's hardware is available to the research community at various levels of computing power, from a 72-processor circuit board capable of simulating 10,000 neurons, to a 921,600-processor machine comprising ten 19-inch rack cabinets and capable of simulating hundreds of millions of neurons.

For now, IBM's TrueNorth chip (estimated computational efficiency and throughput exceed today's GPUs by 340x and 50x, respectively)<sup>21</sup> is the commercial market leader and we expect further market growth as they expand

beyond currently targeted applications, such as the Weather Company where TrueNorth's neurosynaptic system rapidly updates storm-scale models that can help predict weather events at local scales.

#### Novel Device Implementations (Beyond CMOS: New Materials and Structures)

Neural networks with high numbers of active parameters are made possible by modern large graphics processing unit (GPU) clusters. However, new technologies are required to achieve the next several orders of magnitude in energy savings which are measured in terms of computing performance per energy gains.

The most widely researched novel technology for neuromorphic systems is the memristor, a circuit element whose resistance (corresponding to its memory state) is dependent upon its historical activity that allows the implementation of a learning process.<sup>22,23</sup> Consequently, memristors have become popular in neuromorphic implementations because memristor-based circuits can exhibit behavior similar to that of biological synapses controlling brain memory and learning processes. Memristors are energy efficient and can be fabricated in densely packed crossbar arrays that reduce the size and weight, while increasing memory density of a neuromorphic processor (see Figure 2b).

Memristors and other novel device implementations can be fabricated from a variety of materials, some of which have not historically been used in space systems. The reliability and radiation tolerance of many of these materials are becoming increasingly well-characterized, and several material systems of interest have been shown to be tolerant to radiation environments.<sup>24,25,26</sup> The inherent fault tolerance of neuromorphic networks can help mitigate variability among devices in a large array.

Sandia Laboratories' Hardware Acceleration of Adaptive Neural Algorithms (HAANA) program developed a compact memristor-based neuromorphic computer using co-designed hardware—architecture—algorithm systems. This general purpose neural architecture can address cyber security, remote tracking and other applications. Using an analog resistive memory (RRAM memristor) crossbar technology, HAANA requires 430 times less energy compared to a system employing a static random-access memory (SRAM) based accelerator (as in TrueNorth).<sup>27,28</sup> Among a variety of commercially available options in the memristor family, which were not yet evaluated for neuromorphic systems, we should mention an interlocking matrix of NRAM cells made of carbon nanotubes.<sup>29</sup> NRAM has desirable properties for implementation in a host of integrated systems due to its demonstrated advantages of operation, including high speed (switch state in picoseconds), high endurance (over a trillion), and low power (with essential zero standby power).

DARPA initiated a program in 2017 which aims to build the first-ever all-memristor processor. DARPA's project "Foundations Required for Novel Compute" (FRANC) will attempt to realize circuit prototypes beyond von Neumann topologies and will leverage emerging materials and integration technologies. This research project, if successful, will be significant because the industry is reaching the limits of Moore's Law. HRL Labs researcher, Dana Wheeler, noted that "We've known for some time that if you keep cramming components onto a chip and making it faster, eventually it will get hot enough to melt the circuit."<sup>30</sup> A large addressable market exists for highperformance computing applications. Yet the current market challenge for NC, is that the hardware must currently be tailored to specific applications. This implies that the end-user market must have adequate volume to justify the upfront capital investment for custom- or domain-specific NC hardware development. Clearly, space-based applications are a niche market. Therefore, the general consumer market for high-performance NC may eventually blaze the trail for follow-on niche-level markets, such as high-performance on-orbit computing in space.

#### Neuromorphic Commercial and Research/ Nonprofit Implementations

Table 2 lists examples of nonprofit and R&D institutions and commercial providers of neuromorphic engineering solutions. Clearly, "one size doesn't fit all." The range of implementations vary depending upon end-user needs and applications, including: robot control, image and speech recognition, research, and human brain operations. Attributes can also vary depending upon whether the application is mobile or stationary. Example attributes include:

User Applications – What are the targeted applications?

*Energy Efficiency* – Is this a power-efficient solution relative to other existing technology options?

*In-situ Learning and Autonomy* – Does this solution allow the user to perform off-line, without external connection? And without human intervention?

*Implementations* – What hardware technology and software are employed in this solution?

*Mobility* – Is the solution acceptable for mobile applications (mass and size efficient)?

*Market Readiness* – Is this technology ready for market (consumer or government applications)?

# Game Changer Lifecycle: Market and Technology Triggers

Below, we discuss technology triggers that will advance neuromorphic computing:

- Technology triggers for space applications

- Technology triggers to advance maturity in general market

- Market triggers for general market and space applications

#### Technology Triggers for NC in Space Applications

At this point, most systems (see Table 2) have some attributes necessary to operate in space. In addition to energy efficiency, in-situ learning and autonomy, space based NC chips must be "hardened" for a harsh space environment that includes radiation. NC architectures in space must also meet stringent size/weight requirements and retain sizable data with power interruptions. We believe that these challenges are surmountable, as lowpower operations and rad-hardness were demonstrated in well-studied metal oxide materials used in memristor devices and conventional transistors.

Fast learning capability points to memristor-based hardware as a potentially viable technology; however, memristors, which may employ a large variety of materials, have not yet been widely proven to operate in a space environment.

## Technology Triggers to Advance NC Maturity in General Market

The following triggers will advance the technology maturity of NC in the general market:

*Hardware Research Developments* – Need to understand and resolve outstanding issues in NVM (non-volatile memory) technology, such as the read/write operation noise, stochasticity and non-linearity of the memory switching operations that is related to the atomic-level properties of the employed materials. Ongoing research efforts are currently addressing these challenges.

Co-development of Algorithms, Architectures, and Hardware-Enhancing NC Capability – A Department of Energy roundtable of experts<sup>31</sup> concluded that a revolutionary technological leap to a neuromorphic computer is determined by/depends on concluded that a revolutionary technological leap to a neuromorphic computer is determined by/depends on "the development of novel materials and devices incorporated into unique architectures." It points to an accelerating strategy through the convergence of development efforts, including the codevelopment of algorithms, architecture and hardware, combining the expertise of groups/organizations, as was demonstrated by the HAANA program (2017) at Sandia National Labs. Since then, progress has been made to make implementations more effective-particularly an improved understanding of critical materials and operational properties of novel memory (NVM) devices. Significant advances in algorithm development addressed critical issues such as training techniques, visualization of data representations, and learning strategies. To overcome the above "bias barrier," the technology evaluation should be performed comprehensively under the space applicationspecific conditions.

# Market Triggers for General NC Market and Space Applications Market

*Develop Tools and a Robust Community of Users* – Conventional architectures have a robust suite of development tools, along with large numbers of technical staff who are trained in their use. In brief, NC competes for resources and attention from the vast numbers of researchers and users focusing on conventional computing architectures.<sup>32</sup> The user-base needs motivation and incentives to switch to a new and unfamiliar architecture. It remains unknow what that tipping point might bepossibly a practical means of offering significant performance or power advantage.

*High-Volume Consumer Applications for NC* – Commercial players such as IBM, Google, and others will target large consumer markets, which may eventually drive down manufacturing costs of NC hardware. While space typically relies upon small quantities of high-cost parts, the industry is changing rapidly and more commercial grade parts are being integrated into space systems. Also, NC applications will continue to evolve and grow. The space sector niche market will be able to leverage a range of software, algorithms, and applications from high-volume terrestrial market applications.

### Conclusion

Neuromorphic-inspired architectures are aimed to address the shortcomings of modern computing to meet nextgeneration space electronics requirements. Deploying faster, smarter, autonomous, and more power-efficient satellites in space is a significant advantage—for both government and commercial stakeholders. It is reasonable to expect that NC will eventually prove to be a game changer for space operations because it has demonstrated the potential to overcome constraints on power and speed to enable agile information systems.

However, there is much work ahead. The extremely high growth rate of AI in almost every sector of the economy, coupled with the continued expansion of cloud computing, mobile computing, and the IoT will drive R&D funding and commercial incentives to advance the state of play for NC. The successful introduction of NC to space applications will depend on the space sector's ability to "spin-in" NC innovations from the commercial and R&D sector. Much like cloud computing, 3D printing, and artificial intelligence, which began as non-space applications, NC will need to compete for significant R&D funding and commercial investment.

Over time, however, we expect that NC will reach an inflection point where the space sector can take advantage of these technological developments and begin to customize NC architectures for specific space applications and environments. A well-coordinated effort utilizing the most promising technologies and know-how from industry and academia could result in a successful demonstration in space vehicles within the next three to six years.

#### References

- <sup>1</sup> https://www.defense.gov/Portals/1/Documents/pubs/2018-National-Defense-Strategy-Summary.pdf.

- <sup>2</sup> https://en.wikipedia.org/wiki/John\_von\_Neumann.

- <sup>3</sup> Adapted from: Sangsu Park, et al., "Nanoscale RRAMbased Synaptic Electronics: Toward a Neuromorphic Computing," January 2013.

- <sup>4</sup> Tran, A. H., et al., Design of neuromorphic logic networks and fault-tolerant computing, 11th IEEE Conference on Nanotechnology (IEEE-NANO), 2011.

- <sup>5</sup> Taggart, J. L., W. Chen, et al., In Situ Synaptic Programming of CBRAM in an Ionizing Radiation Environment, IEEE Trans. Nuc. Sci. 65(1), 2018.

- <sup>6</sup> Deionno, E., and A. White, "Reliability considerations and radiation testing of memristor devices," Proc. IEEE Aerospace Conference, 2015.

- <sup>7</sup> The Global Exploration Roadmap, January 2018; International Space Station Coordination Group (ISECG), p. 24.

- <sup>8</sup> Cohen, N., R. Ewart, W. Wheeler, J. Betser; "Spacecraft Embedded Cyber Defense- Prototypes & Experimentation," 2016.

- <sup>9</sup> Statistica The Statistics Portal; https://www.statista.com/topics/840/smartphones/.

- <sup>10</sup> McKinsey Global Institute Report; "Unlocking the Potential of the Internet of Things"; 2015; https://www.mckinsey.com/business-functions/digitalmckinsey/our-insights/the-internet-of-things-the-value-ofdigitizing-the-physical-world.

- <sup>11</sup> Boston Consulting Group; https://www.bcg.com/d/press/21june2017-gainingrobotics-advantage-162604.

- <sup>12</sup> Grand View Research; "Neuromorphic Computing Market Size, Share & Trends Analysis Report by Application (Signal Processing, Image Processing, Data Processing, Object Detection) By End Use, By Region, And Segment Forecasts, 2018 – 2024," April 2018.

- <sup>13</sup> https://irds.ieee.org roadmap.

- <sup>14</sup> https://irds.ieee.org.

- <sup>15</sup> Merolla, P. A., et al., A million spiking-neuron integrated circuit with a scalable communication network and interface, Science 345 (6197), 668-673, 2014.

- <sup>16</sup> Ambrogio, S., et al., "Equivalent-accuracy acceleration of Neural Network Training using Analog Memory," Nature, vol. 558, p. 60-67, 2018.

- <sup>17</sup> Furber, S. B., et al., The SpiNNaker Project. Proceedings of the IEEE 102, 652-665, 2014.

- <sup>18</sup> Benjamin, B., et al., Neurogrid: A Mixed-Analog-Digital Multichip System for Large-Scale Neural Simulations. Proceedings of the IEEE 102, 699-716, 2014.

- <sup>19</sup> Schemmel, J., et al., A wafer-scale neuromorphic hardware system for large-scale neural modeling. In Proc. IEEE International Symposium on Circuits and Systems, 2010.

- <sup>20</sup> James, C. D., et al., "A Historical Survey of Neuralinspired Algorithms and Hardware: Architectures for Neuromorphic Computing Applications," Sandia National Labs; SAND2016-12503J; 2016.

- <sup>21</sup> Ambrogio, S., et al., 2018.

- <sup>22</sup> Marinella, M. J., et al., Multiscale Co-Design Analysis of Energy, Latency, Area, and Accuracy of a ReRAM Analog Neural Training Accelerator, IEEE – Circuits and Systems Society; January 2018.

- <sup>23</sup> Prezioso, M., et al., Training and operation of an integrated neuromorphic network based on metal-oxide memristors, Nature 521, 61-64, 2015.

- <sup>24</sup> Taggart, J. L., 2018.

- <sup>25</sup> Deionno, E., and A. White; 2015.

- <sup>26</sup> Jian, R., E.X. Zhang, et al., Total Ionizing Dose Response of Nb2O5-based MIM Diodes for Neuromorphic Computing Applications, IEEE Trans. Nuc. Sci. 65(1), 2018.

- <sup>27</sup> Marinella, et al., 2016.

- <sup>28</sup> Agarwal, S., et al., Resistive Memory Device Requirements for a Neural Algorithm Accelerator, International Joint Conference on Neural Networks (IJCNN) 2016.

- <sup>29</sup> Gilmer, D. C., et al., NRAM: A Disruptive Carbon-Nanotube Resistance-Change Memory, Nanotechnology 29, 134003, 2018.

- <sup>30</sup> HRL Labs (Malibu, CA); www.hrl.com; "All-Memristor Architecture Could Enable Brain-Like Computers" July 24, 2018.

- <sup>31</sup> Neuromorphic Computing: Architectures, Models, and Applications, DOE Workshop Report, 2016.

- <sup>32</sup> Gomes, L., "Special report: Can we copy the brain? The neuromorphic chip's make-or-break moment"; IEEE Spectrum (Volume: 54, Issue: 6, June 2017).

#### **Acknowledgments**

The authors would like to acknowledge contributions from Wally Buell, Erica Deionno, Christopher Silva, Doug Enright, and Brendan Foran.

### **About the Authors**

**Dr. Maribeth Mason** is the director of the Microelectronics Technology Department in the Physical Sciences Laboratories at The Aerospace Corporation. She joined Aerospace in 2003 and has a broad experience with reliability, radiation effects and physics of failure in microelectronic and optoelectronic devices, including advanced CMOS technologies, ASICs, semiconductor lasers and RF devices. Her research focuses on the effects of processing and defects on performance and reliability of devices, and development of laboratory capabilities to locate and quantitatively characterize defects in devices. Dr. Mason earned a B.S. in materials science and engineering from the University of Illinois at Urbana-Champaign, and a Ph.D. in applied physics from the California Institute of Technology.

**Dr. Gennadi Bersuker** is a senior scientist in The Aerospace Corporation's Microelectronics Technology Department, focuses on characterization and reliability of microelectronic devices employed in various space-related applications. Prior to joining Aerospace, he has been a Fellow of the semiconductor industry research consortium SEMATECH, working on the development of advanced technology node devices to identify material atomic features affecting device performance. He is the editor of IEEE Transactions on Device Materials and Reliability and has been involved in many technical conferences, including IRPS, IEDM, APS, IRW, etc. He has published over 450 papers on the semiconductor processing, and reliability, and electronic properties of dielectrics.

**Karen L. Jones** is a senior project leader with The Aerospace Corporation's Center for Space Policy and Strategy. She has experience and expertise in the disciplines of technology strategy, disruptive technologies, program evaluation, and regulatory and policy analysis spanning the public sector, telecommunications, space, aerospace defense, energy, and environmental industries. She is a former management consultant with IBM Global Services and Arthur D. Little, and has an M.B.A. from the Yale School of Management.

### About the Center for Space Policy and Strategy

The Center for Space Policy and Strategy is dedicated to shaping the future by providing nonpartisan research and strategic analysis to decisionmakers. The Center is part of The Aerospace Corporation, a nonprofit organization that advises the government on complex space enterprise and systems engineering problems.

The views expressed in this publication are solely those of the author(s), and do not necessarily reflect those of The Aerospace Corporation, its management, or its customers.

For more information, go to <u>www.aerospace.org/policy</u> or email <u>policy@aero.org</u>.

© 2018 The Aerospace Corporation. All trademarks, service marks, and trade names contained herein are the property of their respective owners. Approved for public release; distribution unlimited. OTR 201800719